Tutorial on getting started in Cadence Advanced Analog Circuits Spring 2015 Instructor: Prof. Harish Krishnaswamy. Start Cadence from the terminal by using the command virtuoso. Click Tools-Library Manager. Virtuoso Spectre Circuit Simulator RF Analysis User Guide Spectre RF Simulation Form Reference. June 2007 52 Product Version 6.2. To specify the listed sidebands, 1. In the From (Hz) and To (Hz) type-in fields, type the lower and upper values for the frequency range.

In this tutorial you will go through creating an Inverter layout while performing design-rule checks (DRC). This tutorial assumes that you have logged in to an EOS machine and are familiar with basic UNIX commands.

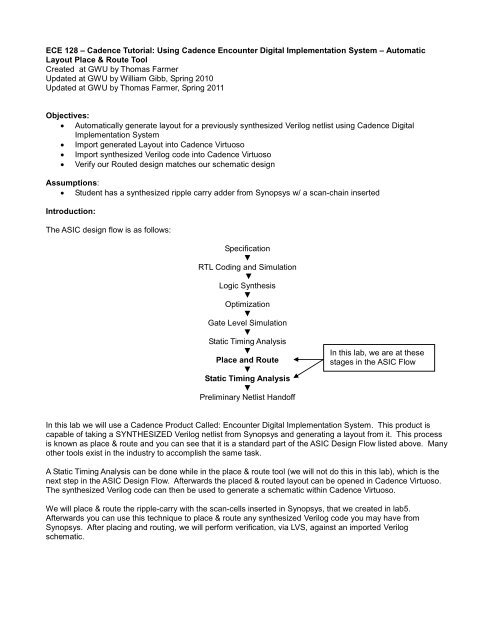

- 2Start the Cadence Design Framework

- 4Create Layout View of an Inverter

- 6DRC

- 7Painting

Create Aliases to Setup Your Environment

Before you start this tutorial, add the following line to the .bash_profile file in your home directory:

The line defines an alias that gives a command to setup your environment to use the FreePDK15 design-kit with the Cadence tools. You can set up other design-kits with other commands (such as 'add cadence_cdk', which sets up the Cadence Design Kit for the MOSIS technologies). If you regularly use machines that default to the tcsh shell (rather than bash), then you might want to also add the following line to the .mycshrc file in your home directory, which does the same thing for that shell:

Before moving on, source your .bash_profile (bash) or .mycshrc (tcsh) file or log out and log back in.

Note to users outside NCSU:The setup.sh scripts mentioned above is provided in $PDK_DIR/cdslib/setup/setup.sh.

Start the Cadence Design Framework

- Log in to a Linux machine. The setup for this tutorial is currently supported only on Linux machines.

- Create a directory to run this tutorial, called something like 'layout1'. Change to this directory.

- Type 'add cadence2018 calibre2018.2' at the command prompt. This will add the Virtuoso and Calibre tools to your search path. We will use Virtuoso to edit the layout and Calibre to run design-rule checks.

- Type 'setup_freepdk15' at the command prompt. This will setup your directory by copying in various files that are needed to run the Cadence tools, including .cdsinit and cds.lib.

- Start the Cadence Design Framework by typing 'virtuoso &' at the command prompt.

If you haven't done Tutorial 0 (Analog Artist with Hspice) then you would need to create the following. If you have please go

The first window that appears is called the CIW (Command Interpreter Window).

Another window that is very handy is the Library Manager, which allows you to browse the available libraries and create your own. To display this window, choose Tools -> Library Manager... from the CIW Menu.

Start the Cadence Design Framework from Tutorial 0

For ECE546 students you have already created a directory called adetut, you can simply go to the linux command line one directory above the adetut (or whatever your main project directory was named) folder and type

NOTE: If you haven't properly defined items in your cds.lib path to be a relative path, you might not see your ADETutorial Library. Chances are, you probably lost points on your Homework 1 as all of these paths were told to be relative and not absolute paths. Edit the cds.lib file to ensure that it is appropriate!

NOTE: This is probably a good time to mention, that for your homework, you could once again rename this using the cp -r command to cp -r layout1 to homework2. Then inside of this, if you need to make multiple testbenches for multiple problems, then you can use the copy and rename commands introduced in this tutorial to save time. Naming different testbenches based on the problem number.

Migrate From Analog Artist with Hspice tutorial for Layout View of an Inverter

If you have done Analog Artist with Hspice tutorial prior to this Tutorial, then you should continue working on your previous work. We will introduce you on how to copy libraries and rename cellviews. So, before you continue, you may want to back up your design in the Tutorial of Analog Artist. This would be a good time to setup a github repository. For NCSU Students there is a http://github.ncsu.edu that is available to you.

Here is how you can quickly copy your own library in the tutorial of Analog Artist.First of all, right click the library you have created in your very beginning tutorial. Here I named it as “ADETutorial”. By right clicking on it, you can see a menu. Hit copy, and then it will pop out the dialogue shown below.

NOTE: the pictures need to be updated to reflect mylib instead of myLib

You need to do two things: 1. Change To Library name as mylib, or any other name you feel more comfortable with; 2. Check the Options and select Update Instance as Of New Copies Only. As both steps are done, click OK. Then the new library mylib will be duplicated in short.

To follow up, you should rename your previously designed inverter in your newly created library mylib. Now, left click “mylib” to select this library, and then under its Cell, right click myInverter(Let’s say you have named your inverter as this name in your very beginning tutorial), and choose “Rename” in the right-click menu. Then there will be a dialogue popped out, as below:

NOTE: The image needs to update the picture to show inv instead of myInv. Again, you should name this as inv so that when you create the layout you will end up having the schematic, symbol, and layout all in a single cell with multiple cell views. This will allow you in the next tutorial to create an extracted view inside the inv cell and simulate easily.

Now you can rename it as inv. When you have done the renaming, you can start creating the layout of your inverter here.

Create Layout View of an Inverter

Create New Library

NCSU 546 students should have migrated the ADETutorial creating the mylib library and the inv cell. In which case, skip to the next part Create New Layout View.

In the Library Manager, create new library called mylib. Select File->New->Library. This will open new dialog window, in which you need to enter the name and directory for your library. By default, the library will be created in the current directory. After you fill out the form, it should look something like this:

Click OK. Next, you will see a window asking you what technology you would like to attach to this library. Select 'Attach to an existing technology library' and click OK. In the next window, select 'NCSU_TechLib_FreePDK15'. You should see the library 'mylib' appear in the Library Manager.

Create New Layout View

Next, select the library you just created in the Library Manager and select File->New->Cell View.... We will create a layout view of an inverter cell. Simply type in 'inv' under cell-name and 'layout' under view. Click OK or hit 'Enter'. Note that the 'Application' is automatically set to 'Layout L', the layout editor.

Alternatively, you can select the 'Layout L' tool, instead of typing out the view name. This will automatically set the view name to 'layout'.

Click Ok. You may see a warning about upgrading the license. Simply click Ok to ignore this warning. After you hit 'OK', the Virtuoso screen will appear as shown below.

Now you are ready to draw objects in the Virtuoso window. In this section you learn to place copies of other cells: pmos_pcell and nmos_pcell. These cells are parameterized cells (or p-cells) which change their features when you change their parameters.

In Layout Editor select Create->Instance, or simply hit 'i'. This will pull up the 'Create Instance' dialog box. Next, click 'Browse' on the screen that appears and select the library 'NCSU_TechLib_FreePDK15', cell 'nmos_pcell', view 'layout'. Click 'close' on the browser window. Then expand the parameters section of the create-instance dialog to look for parameters called nFins and Gate. Make sure these are set to 2 and A, respectively.

Next, move the cursor into the layout editor window. You should see a small instance at the tip of your cursor, as shown below.

You may want to zoom in before placing the instance. To do that, right-click and drag a box around the origin, as shown below. When you release the button, you should see that the instance is much larger.

Next, place the NMOS transistor so that your layout looks like the window below. Make sure to place it exactly on the y-axis as shown below, which will make things easier later-on. Next, in the create-instance dialog box, change the cell from 'nmos_pcell' to 'pmos_pcell'. Place the pmos roughly as shown below, also on the y-axis. Finally, hit 'Escape' to stop adding instances.

Now, you will notice that you don't immediately see what is inside the nmos_pcell symbol. You can fix this by hitting Shift-F to display all levels of hierarchy. (You can also do this by going to the Virtuoso Options menu, choosing Display and setting Display Levels from 0 to 32) To switch back, hit CTRL-F, or set the Display Levels back to 0 from the Options menu.

You may want to adjust your view so that it looks nicer. To zoom in, right-click and drag a box around the area you want to zoom in. Alternatively, you can hit 'f' to 'fit' the entire design in the window, or SHIFT-Z and CTRL-Z to zoom in and out by factors of 2.

Use the commands above to show the layout as below.

Now, look now at the 'Layers' box on the left side of the layout window (which was referred to as the 'Layer Selection Window' or LSW in older versions of Virtuoso). This box shows you the names of the layers that are 'valid' (meaning that you can manipulate them). You can figure out which layers are part of the NMOS cell by making them visible and in-visible. To toggle a layer’s visibility, click the 'V' check-box to the right of the layer's name. You can make all layers visible with the 'AV' button, and no layers visible with the 'NV' button. Sometimes, you may need to hit F6 to 'redraw' the Virtuoso window after you’ve changed the visible layers. You can use the 'Used Layers Only' check-box to limit the number of layers listed to include only those layers that are used in the current layout.

Note that even if you make all layers invisible, you may still see some shapes. This is because not all layers are 'valid'. Shapes in invalid layers cannot be altered and are always visible. To make all layers valid, you can right-click on the 'Used Layers Only' label and choose Edit Valid Layers…. In general, it is recommended that you not set all layers as valid, because this clutters up the Layer list with many unused layers.

Using this approach, you should be able to figure out that the NMOS uses the following layers: ACT, NIM, GATEA, GATEB, and AIL1. The PMOS is like it, except that it uses layers PIM and NW and omits NIM. Note that there is nothing magical about this instance. You could paint these shapes manually in the current cell-view, and it would make no difference whatsoever to the tool. However, it’s much less effort to use this instance, so that’s what we’ll do.

Note also the letters 'drw', 'net', or 'pin' next to each entry in the layer list. These are the purposes of a shape. The purpose is used to indicate special functionality of a shape. We will discuss these more in later tutorials. For now, remember that 'drawing' is the purpose that indicates that a shape will appear in the mask layout. You will sometimes see 'drawing' abbreviated as 'drw', and sometimes 'dg'.

Selecting and Moving Layout

By default, if you simply drag out a region while holding down the left mouse button (Button-1), whatever is within the box will be selected and highlighted in white.

- Drag a box over the nmos you just instantiated. When you release the mouse button, whatever is 'selected', in this case the nmos_pcell cell, will be highlighted.

Once you have selected an object (that is, an instance or a shape) you can do lots of things with it.

- For example you can move it by typing the m hot-key. You can move layout up/down/left/right one grid at a time by clicking at the selection and moving the mouse. Try it.

You can also select objects by clicking on them.

- Clicking the left mouse button once on an instance or shape selects it.

If you didn’t place your NMOS and PMOS cells exactly as illustrated above, try moving them now until they are.

Next, place instances of three vias (this should be shortcut key O), as shown below. The top and bottom instances will be M1A_AIL2 and will connect to the active areas. Make sure that the AIL2 shapes on the via are perfectly centered inside the AIL1 shapes on the mos-devices. The middle instance will be M1A_GIL, which will eventually connect to the gate. Make sure that its M1A shape is perfectly aligned with the other two vias.

DRC

To perform a Design Rule Check (DRC), choose Calibre->Run DRC…. The DRC form appears, as shown below. Then click 'Run DRC'. If you do not see the window appear, or if you get an error, then it's possible that you didn't type 'add calibre' as instructed above. You will need to exit Virtoso, log out, and log back in, setting up your environment in the correct order. If you still don't see it, try typing 'mgc_calibre_run_drc' in the CIW.

Viewing DRC Errors

You can learn about the errors by clicking on the rule in the Results Viewing Environment (RVE) window that pops up after DRC is complete. Double-click on one of the two M1004A errors (or single-click and hit 'shift-H') to highlight the error in the layout viewer as shown. NOTE: This should work as described by default, but if it doesn't, in the DRC RVE window, choose Setup->Options..., select 'Zoom cell view to highlights by 0.7', and click 'OK'. You should only need to do this once. Your choice will be saved for the next time that you log in.

In this particular case, the M1A shapes are too close together. To fix this error, you'll need to move the instances further apart. It’s good practice to space the vias by the smallest amount allowed in order to make the layout as dense as possible. You can draw temporary rulers by hitting 'k' and dragging a ruler. You can clear the rulers by hitting 'Shift-K'. These rulers can help you to draw dense layout much faster than you would by constantly running DRC.

You should note that the ruler can do many different measurement functions. You would be wise to explore the manual located in $CDS/IC/doc you are looking for the vlehelp folder (find $CDS/IC/doc -name '*vlehelp*' will locate it and you should use this for finding other manuals such as viva the schematic editor (comphelp is the name of the Virtuoso Schematic Editor L). You should look at: Using Rulers (this one is important), Creating Rulers with Smart Snapping, Setting Up Snap Mode, Creating Rulers with Snapping On, and a whole host of others. With rulers, you can cycle through the snap modes (anyAngle -> diagonal -> orthogonal) by pressing the N bindkey or clicking the Synchronized SnapMode icon on the Options toolbar.

Move the vias and re-verify until there are no DRC errors. You can re-run DRC by simply clicking on 'Run DRC' in the DRC Form window. You will be asked if you want to overwrite the layout file (inv.calibre.gds). Click Ok. Virtuoso is exporting a file to Calibre every time you run DRC. Note that you will need to save your layout each time you run DRC. Otherwise, the check will run on the last layout you saved. If you simply want to remove the error markers, choose Highlight->Clear Highlights… in the RVE, or click on the button that looks like an eraser.

Keep modifying your layout until the M1004A error disappears, and move the pmos_pcell cell to stay aligned with its via. To learn more about each design-rule, find the complete list of the current rules in the FreePDK15 Table of Contents). This page gives the name and value of every rule. Note that the rule names are slightly from what is displayed in the RVE, such as M1004A which appears as M1.4.

Once you are done, your layout should look like the one below:

Now let's look at the remaining errors. Here we're using the name as they appear on the web-page (rather than the RVE), for easy reference.

- ACT.9 - This is a rule to prevent latch-up. We'll need to create well-contacts later to solve these errors.

- NW.4 and NIM/PIM.7 - These are minimum-area rules. We could fix them now by drawing larger NW/NIM/PIM boxes around the current ones. However, since we still have more NW, NIM, & PIM shapes to make (for the well-contacts), we can put these off until later to save effort.

- GIL.2 - This rule shows that the M1A_GIL via is not entirely error-free. In particular, the GIL shape is not wide enough. The via was designed this way, because GIL is generally used for horizontal routing. When we paint shapes, we'll extend the GIL shape on the via to the right, to connect to the gate.

Before we start painting, we have to make some changes. First, we have enough space to add more fins on our transistors, so let's do that. Fortunately, our p-cells make that easy to do. Simply select each instance and select Edit->Basic->Properties (or press 'q'). Select the Parameters tab on the properties dialog-box and change nFins to 3. Then click Apply or Ok. You will see the transistor shape update to include a third fin. Note that you can also select whether you want the gate shape to be drawn in GATEA or GATEB with the Gate parameter. Re-run DRC to make sure that you have not violated the ACT.2 rule. When done, it should look like the image below.

Finally, we'll need to add contacts for the drains. Add two instances of M1B_AIL2 as shown below. Make sure that they are centered on the AIL1 shapes in the mos-devices.

Painting

We are now going to 'paint' a line to connect the pmos and nmos devices together. We do this by creating a shape, in this case, a rectangle.

- Select the GATEA layer in the layer list by left-clicking on it.

- Hit “r” to draw a rectangle and draw the GATEA area.

- Hit “Escape” to stop drawing rectangles.

- Your layout should look like this:

If you don’t like the way your drawing turned out, you can select a shape and delete it with the delete key, or you can hit “s” (for stretch), and click on one of the sides of a path or rectangle to stretch it into the position that you like. In some cases, if the object doesn't stretch, you might try clicking the corner of the object and see. You will know the object can stretch by hovering over the side/corner and it should indicate by highlighting that side or corner.

Also, you may want to run DRC checks periodically to make sure you're making progress in good direction. It’s also a good idea to save occasionally, by selecting File->Save.

Go ahead and create rectangles of GATEB to connect the other gate-lines, as well as a rectangle to connect the M1B vias as shown below. Finally, create a rectangle to extend the GIL shape to the right as shown below. Re-run DRC and fix any errors that you find (except for the ACT.9, NW.4, and NIM/PIM.7 rules, which we will get to next).

Other Ways to Create Shapes

Here are some other ways to create shapes that you may want to try:

- Path - You can draw a path by selecting the entry layer and then choosing Create->Shape->Path (or press 'p'). Then click wherever you like in the layout. A minimum-width path will be drawn. This is mostly convenient for higher levels of metal, which don't usually have different width rules for different routing directions.

- Copy - You can copy a shape or instance with the following steps:

- Selecting the shape/instance

- Choose Edit->Copy (or press 'c')

- Click on the shape/instance to set a reference point for the copy

- Drag the mouse to the location of the copy

- Click again to place the shape/instance

Create Well Contacts

Now let's solve those latch-up errors. Do that by creating the following instances, such that your layout matches the one below:

- Add AIL1_N to connect to the n-well. Make sure that its ACT shape is exactly 96nm away from the PMOS ACT shape, to satisfy rule ACT.5.

- Add AIL1_P to connect to the p-well. Make sure that the right side of its PIM shape is exactly aligned to the left side of the NIM shape on the AIL1_N instance, for maximum density.

- Add two instances of M1A_AIL2. Make sure the AIL2 shapes are centered on the AIL1 shapes for the well contacts that you just made.

Now let's solve those remaining DRC rules. Create rectangles of NW, NIM, and PIM to match the layout below. Remember that the minimum width of NIM & PIM is 128nm (rule NIM/PIM.1) and that the NW shape should be 31nm away from the ACT shape in the p-well contact (rule ACT.7). Keep modifying your layout until there are no more errors. You will know that there are no errors when there are no red boxes in the RVE. Alternatively, you can look in the file inv.drc.summary. When the layout is 'DRC Clean', the last line of this file should read 'TOTAL DRC Results Generated: 0'.

Finally, create strips of metal1 for VDD and GND. We typically make these shapes as horizontal bars across the top and bottom, and therefore call them “supply rails”. We then need to connect the rails to the source nodes of the transistors. Create these rails now, and make your design look like the one below. Again, try to make the layout as compact as possible and the supply rails as thin as possible, running DRC as often as needed to learn the design rules.

Create Pins

Lastly, we need to create pins so that the nodes in our layout have names that are human-readable. Create these pins by selecting Create->Pin…. You should see a dialog box appear, like the one below. Type the names vdd!, gnd!, in, and out in the “Terminal Names” text-box as shown below. Select “Create Label”. Leave all other options as they are.

Next, click the “Options…” button next to 'Create Label'. You will see another dialog box appear:

Set the height to 0.02 um and the 'Layer Name' to 'Same As Pin'. Click OK. Make sure that you have M1A-drw selected as your entry layer.

Cadence Virtuoso Tutorial Pdf Online

Next, click on the layout where you want the vdd! pin to be placed. You will need to click three times: twice to create a rectangle for the pin, and a third time to place the label. The shape of your rectangle doesn’t really matter, as long as it only covers area that is already covered by M1A-drw. Repeat this procedure for the gnd! and in pins. Before adding the out pin, make sure to change the entry layer to M1B-drw. When you are done, your layout should look like the one below (with NW, NIM, and PIM set invisible, for clarity).

Important Note: It is absolutely essential that you select the Create Label box when you create each pin. The label must be in the same layer as the metal shape and must overlap the shape. This is necessary to pass Calibre LVS. This is not needed to finish Layout Tutorial #1; however, if you do not get into this habit now, then you will not be able to finish Layout Tutorials #2 and #3.

Congratulations! You have completed the tutorial. Save your design and take a screen-shot of your layout to turn in with your assignment.

ECE 546Students:Hand-in this image of your layout. Make sure that your layout is as dense as possible. Points will be deducted for layout that is larger than necessary.

Further Reading

If you would like to learn more about the layout editor, you can read through the Virtuoso Schematic Editor L User Guide that comes with the Cadence documentation. Start the documentation browser by typing

at the command prompt, and then selecting Virtuoso Layout Suite->Virtuoso Layout Suite L User Guide in the browser window that appears. This should display the pages that you select.

If you find that you cannot view the figures correctly in the web browser, you can browse to the documentation directory in...

...where you will find PDF files for all of these documents. The cdnshelp documentation browser offers many more links for you to learn about the Cadence Design Framework.

- Interactive viewing and editing of hierarchical layout

- Hierarchical and incremental DRC

- Built in netlisting

- Interactive connectivity tracing

- Interactive wiring tool

- Interfaces to other tools, including schematic capture (e.g. Analog Artist), and batch DRC and LVS (e.g. Calibre)

- Smart palette for easy control and feedback on layers

- Full customization and extension via Tcl/Tk scripting language and API

- Technology independence via technology description files

- Optimized for large databases

- Very Fast Redisplay for Whole Chip Viewing and Inspection

- Reads/writes GDSII

- Runs on Solaris and Linux operation systems.

From the icfb window, bring up Library Manager from the Tools menu (select Tools/Library Manager; automatically starts after starting icfb)

Tutorial Ppt

Click 'OK'- Create layout view of your NAND cell. Simply type in 'nand2' under cell name and 'layout' under view. Hit 'Enter', following window will pop up:

Select 'Virtuoso' tool, View Name is automatically set to 'layout'

After you hit 'OK', Virtuoso screen will appear as shown below (in addition, LSW window with various mask layers will automatically pop up):

In this window, you will place transistors, draw mask layers etc.

Virtuoso Screen Layout

On the very top of the window the title bar should say ' Virtuoso Layout Editing: ee141_lab2 nand2 layout '.

Cadence Virtuoso Tutorial Pdf Tutorial

The Palette

LSW window is the Smart Palette. The Smart Palette provides many features.

- It controls which layers are visible, and lets you choose layers for 'painting'.

- It gives feedback on what is currently under the cursor, and what is currently selected.

- It allows you to control which layers can be selected.

Layers

Description of various mask layers can be found at: <file:/usr/eesww/cadence/NCSU_CDK/doc/layerInfo.html> Note: you can access this file only from your Unix account.Use drawing (dg) layers for drawing transistors.

Getting Help

Before we go any further, here is how to get help if you ever need it.

Before proceeding you should bring up the Virtuoso Manual and see what's there. The manual is the reference to Virtuoso and it contains lots of information that you will not find in this simple tutorial.

OK, let's get started on some layout.

- Go to the Virtuoso window and hit 'i' (instantiate)... . This will bring up the following window, click on 'Browse' and select 'NCSU_Tech_Lib_03d':

Next, select 'nmos' from the NCSU_TechLib, the selection should look like this:

Click Close and then go back to the previous window and click Hide, position your cursor in Virtuoso window where you want your nmos placed and click.

Cadence Virtuoso Tutorial Pdf Download

Now, you will notice that Virtusoso works with grid, which is by default very crude. Also, you don't immediately see what is inside nmos symbol. Let's fix this: from the Virtuoso Options menu, choose Display and set Display Levels from 0 to 10, and also X and Y Snap Spacing to 0.06 (this 0.06 is half-lambda, lambda is 0.12 in this 0.24um technology). Your display settings should be as follows:

Click Save To and then OK. Now you can see mask layers in the nmos, you will later realize that you will be able to place your components on a grid with much finer precision, the precision of half-lambda (0.06).

Your nmos transistor probably looks very small on the screen, hit z (zoom in), then hold left mouse button to select the area you want to zoom in. The zoomed-in nmos should look like this:

Note that only 'active' layer is used and this is OK. (There is no p-well since this is p-substrate process.) Read more about layout macros (also known as pcells) such as nmos at file://usr/eesww/cadence/NCSU_CDK/doc/cdsuser/virtuoso.html#tagpcell

Now, edit instance properties, click on the nmos, when the transistor is highlited, hit q. Click on Parameters and change the width to 1.98u (2.0u will be automatically changed to 1.98u due to the grid rules). Since we eventually want to use this device to make a 2 input NAND gate, change fingers to 2.

Now Click OK.

Two nfet's merged (stacked) together should appear.

- Type f ( the hot key for fit all -- zoom to fit under the Window menu) and the layout should appear centered in the window.

TIP! You can undo whatever you have just done in Virtuoso. Use the u hot key or select Undo from the Edit menu. You can also Redo what you have just undone using the Shift-u hotkey.

Zooming

- Now zoom back by typing shift-z, or use Zoom out in the Window menu.

There are several methods for zooming found in the View menu.

- Type z. This puts you in zoom mode. Note that the cursor has changed. Next hold down the left mouse button (Button-1) and 'drag' out a box which surrounds the region you wish to zoom to. When you release the mouse the screen will zoom to where your box was.

- If you mess up don't panic. Remember, f will always zoom to fit.

The hotkey shift-z can be used to zoom out by a factor of two.

Selecting and Moving Layout

- Drag a box over the stacked nfet's we just drew. When you release the mouse button, whatever is 'selected', in this case the fet cell, will be highlighted.

Once you have selected an object or paint you can do lots of things with it.

- For example you can move it by typing the m hot-key. You can move layout up/down/left/right one grid at a time by clicking at the selection and moving the mouse. Try it.

You can also select objects or paint by clicking on them.

- Clicking the left mouse button once on a piece of paint selects that particular rectangle of paint.

- Clicking once on a polygon or cell will select the object.

Duplicating Layout, Cut, Copy and Paste

Virtuoso supports Cut, Copy, and Paste in the same format you would see on any good Mac- or PC-based drawing or painting program.

TIP! All of the zoom, move, cut and paste, rotate, etc. features that we just executed using hot keys also have menu equivalents which can be found in the Edit menu.

DRC

To perform a Design Rule Check (DRC), choose Verify/DRC.The DRC form appears:

Click OK to run DRC. There shouldn't be any errors marked on the screen.

Now, add a pmos transistor with a width of 4 microns and Multiplier equal to 2. Place it close to the nmos as shown below:

Choose Verify - DRC and hit OK. You will likely see some DRC errors, marked as white lines on the screen.

Viewing DRC Errors

Use the Verify - Marker - Explain to see more details about flagged errors.

Errors are described in the marker text window like this one.

In this particular case, Source/Drain active was too close to the n-well edge. Minimum required spacing of 0.7um is required. Fix this error by moving up the pmos.

Esc cancels the explain command, the marker text window will disappear. To remove error flags, choose Verify - Marker - Delete all

Hit OK to delete all error flags.

Painting

We are now going to 'paint' a piece of poly to connect the pfet and left nfet gates together.

- Select poly layer from the palette, hit r to draw a rectangle and draw the poly area. Your layout should look like this:

Wiring

Using r and p hotkeys to draw rectangles and paths, wire up the two left contact regions and add the connection to the right pfet contacts. If you have trouble with the p command see the next section for some hints. Consult CDK manuals if needed. Your layout should look like this (practical advice: run DRC check periodically to make sure you're making progress in good direction):

- Type F2, or select Save from the Design menu (also a good thing to do occasionally).

Adding the Power Rails

Let's say we were laying out this NAND gate for a standard cell library. Furthermore, assume that the power and ground rails are run in metal 1 (M1) and that they are 2.04um wide (2.0um won't work because of the grid granularity, which is 0.06um...).

- To add the M1 power and ground wires:

1) Set metal1 as an active layer in the LSW window.

2) Type p to bring up the 'Create Path' menu.

3) Set 'Width' to 2.04.

4) Draw the path where you wish to place Vdd.

- You can always select again the path you drew and type q to change its properties.

TIP! You can change the size of a path or a rectangle by stretching an edge using the Stretch command found in the Edit menu. Simply type s. The cursor changes to let you know you are in Edit Edge mode. Now move the finger over the edge you wish to stretch. A line will show you which edge you are over. Once you have the edge you want click the left mouse button (Button-1) and move the mouse in the direction you wish to stretch the edge. (Note that in a path you can change only the length this way - for the width use q and the properties menu).

Once you have drawn the top power line you can simply copy it and move it down.

When designing various cells (nand, nor, inv) keep the overall cell height constant.

Your cell should look like this:

Wiring Mode - Changing Layers

Notice that the inputs and outputs are all found within the power straps. What if they need to be brought out so a router can get to them?

Using the p command, extend both poly lines over the Vdd strap and end them with M1. Your layout should now look like this (run DRC to make sure it is DRC-clean!):

Labels

There is one last thing before we are finished with our NAND gate.

Click the button next to 'shape pin' to open the Create Shape Pin form:

In the Create Shape Pin form, type the following in the Terminal Names field:

vdd! gnd! Out In1 In2

Click Display Pin Name to associate the name with the pin.

1) Create the rectangle for the vdd! pin coincident with the power line at the top of the NAND. (start the vdd! pin at the lower- left corner and finish the vdd! pin at the upper-right corner).

2) The name vdd! appears near the cursor after you click the second corner (the upper-right corner).

3) Move the cursor to place the vdd! text at the desired place, then click to place the pin name there.

4) If the text looks too big you can select it, type q to bring up the property box and edit its height.

Continue with steps 1-3 above to create other pins in specified sequence (vdd! gnd! Out In1 In2). After you are done, your layout should look like this:

Our little NAND gate example should now be done.

Finishing Cell

We are getting ready to finish this cell. You should add substrate and well contacts (Hint: use ptap and ntap p-cells). You can try to make the cell as compact as possible, so it can be tightly abutted.

Your layout should now look similar to this:

Now let's use our NAND gate and an inverter (which you need to create. Hint: simply copy and modify the NAND...) cell to build something a little bigger.

- In the Library Manager, create new cell named 'row'

Instantiate NAND four times and inverter once to form an array of cascaded cells.

Your layout will look something like the figure above unless you selected to view all the internal layers.

Show/Hide Internals

You may now want to see what's inside of the NAND2 cells and the inverter.

- To do this, hit hotkey e and set Display Levels from 0 to 10, for example.

- This will show all the layers inside the cells as shown below:

Push, Pop, and Edit in Place

OK, now that we are here, let's say our boss comes over and says 'sorry but you need to double the number of substrate/well contacts'.

- First, select the nand cell using and hit hotkey x (for Design - Hierarchy - Edit in Place).

- Add new taps.

- Save the cell and type B (capital!) to get back up.

- Notice that all four instances will be updated -- this is expected since you modified NAND cell from your library. You can open NAND cell to check this out).

- Now that row is your edit cell, simply use wiring strategy you learned in this tutorial to hook up a couple of wires.

To learn more about Virtuoso and other tools just type cdsdoc at your Unix prompt, and the documentation browser should appear.